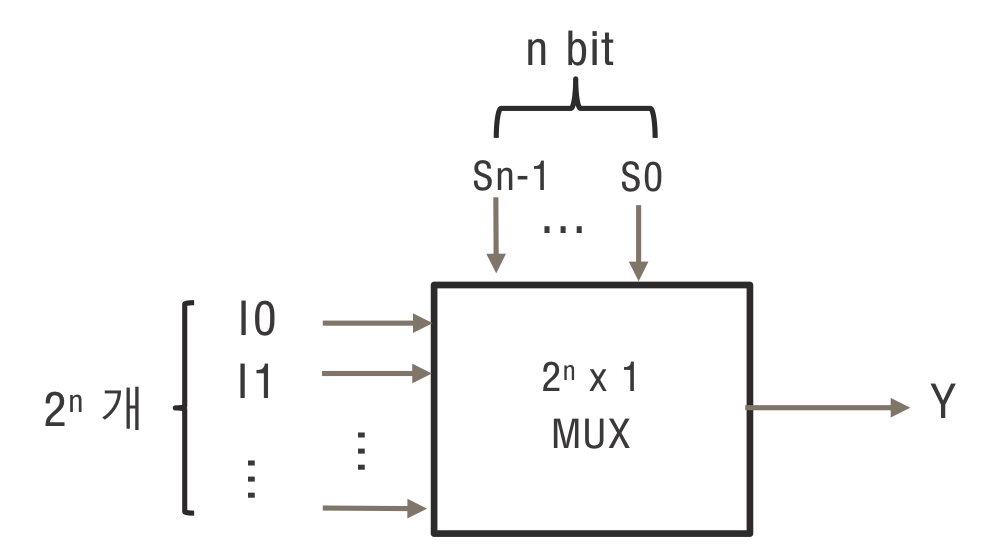

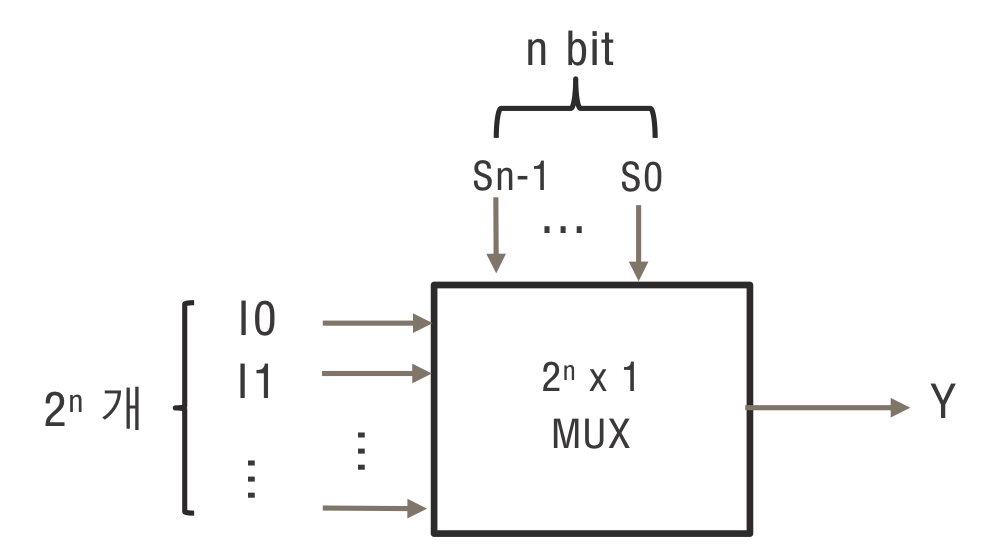

MUX(Multiplexer)

- 여러개 입력 중 제어신호에 의해 선택된 입력을 출력한다.

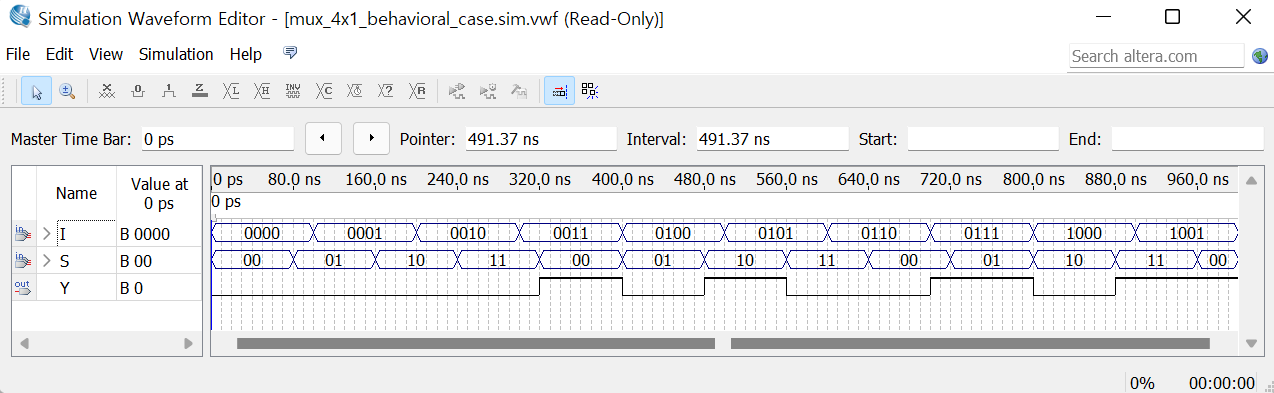

- 4x1 mux이라고 가정하면 input으로 4비트가 들어오고 제어신호에 의해 선택된 부분을 출력한다.

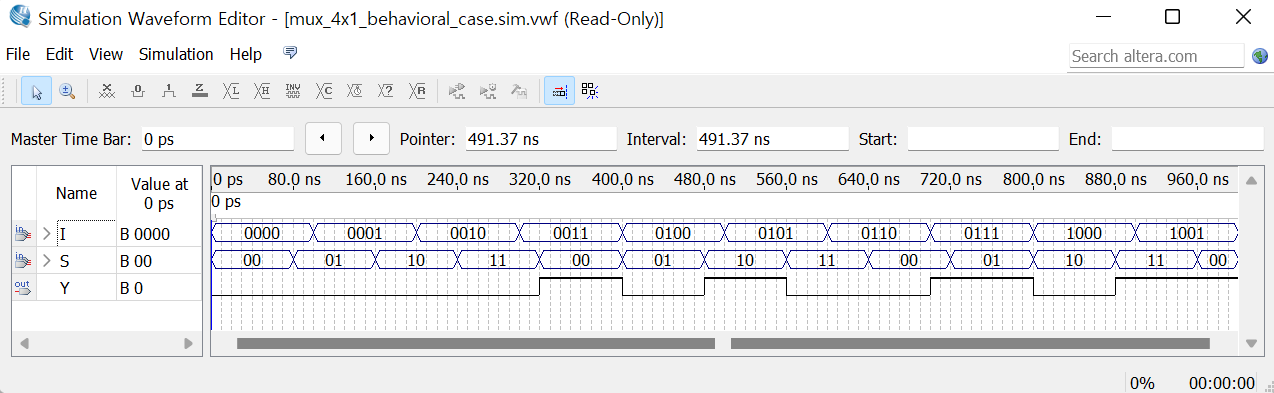

시뮬레이션 결과를 보면 input 4비트와 S라는 선택신호에 의해 00이면 0번비트, 01은 1번비트, 10은 2번, 11은 4번비트를 출력시키는 동작을 보여준다.

1) mux를 if문으로 작성하면 다음과 같다.

//if문

library ieee;

use ieee.std_logic_1164.all;

entity mux_4x1_vhdl is

port( I : in std_logic_vector(3 downto 0);

S : in std_logic_vector(1 downto 0);

Y : out std_logic);

end mux_4x1_vhdl;

architecture dataflow of mux_4x1_vhdl is

begin

process(I,S)

begin

if(S="11") then Y <= I(3);

elsif(S="10") then Y <= I(2);

elsif(S = "01") then Y <= I(1);

else Y <= I(0);

end if;

end process;

end dataflow;2) case문으로 작성하면

library ieee;

use ieee.std_logic_1164.all;

entity mux_4x1_behavioral_case is

port( I : in std_logic_vector(3 downto 0);

S : in std_logic_vector(1 downto 0);

Y : out std_logic);

end mux_4x1_behavioral_case;

architecture behavioral_case of mux_4x1_behavioral_case is

begin

process(I,S)

begin

case S is

when "11" => Y <= I(3);

when "10" => Y <= I(2);

when "01" => Y <= I(1);

when others => Y <= I(0);

end case;

end process;

end behavioral_case;3) when else 문(조건병행신호배정)으로 작성하면

// when ~ else문(조건병행신호배정)

library ieee;

use ieee.std_logic_1164.all;

entity mux_4x1_dataflow_when_else is

port( I : in std_logic_vector(3 downto 0);

S : in std_logic_vector(1 downto 0);

Y : out std_logic);

end mux_4x1_dataflow_when_else;

architecture dataflow of mux_4x1_dataflow_when_else is

begin

Y <= I(3) when S="11" else

I(2) when S="10" else

I(1) when S="01" else

I(0);

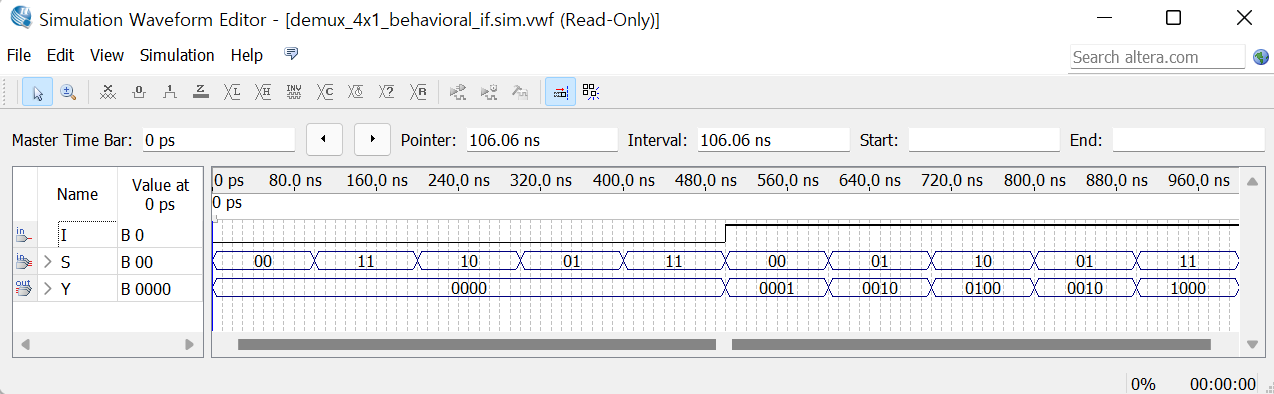

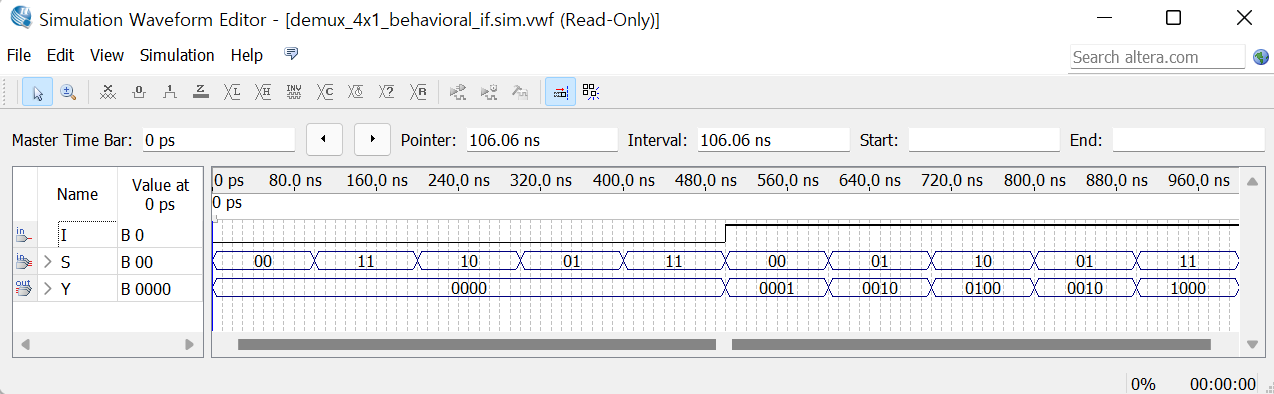

end dataflow;DEMUX(demultiplexer)

- mux와 반대로 하나의 입력신호와 제어신호에 의해 original신호의 몇번비트였는지 알려준다.

input으로 0이 들어오면 아무 값도 없기 때문에 S로 선택해도 0으로 출력되고 1이 들어오면 선택을 해서 특정 비트 위치에 1을 출력한다.

demux를 vhdl로 작성하면 다음과 같다.

1) if문 이용(순차)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_behavioral_if is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_behavioral_if;

architecture behavioral of demux_4x1_behavioral_if is

begin

process(I,S)

begin

if (S = "11") then Y <= I & "000";

elsif (S = "10") then Y <= '0' & I & "00";

elsif (S = "01") then Y <= "00" & I & '0';

else Y <= "000" & I;

end if;

end process;

end behavioral;2) case문 이용(순차)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_behavioral_case is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_behavioral_case;

architecture behavioral of demux_4x1_behavioral_case is

begin

process(I, S)

begin

case S is

when "11" => Y <= I & "000";

when "10" => Y <= '0' & I & "00";

when "01" => Y <= "00" & I & '0';

when others => Y <= "000" & I;

end case;

end process;

end behavioral;3) with ~ select ~ when(병렬)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_dataflow_with_select_when is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_dataflow_with_select_when;

architecture dataflow of demux_4x1_dataflow_with_select_when is

begin

with S select

Y <= "0001" when "00",

"0010" when "01",

"0100" when "10",

"1000" when "11",

null when others;

end dataflow;4) when ~ else(병렬)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_dataflow_when_else is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_dataflow_when_else;

architecture dataflow of demux_4x1_dataflow_when_else is

begin

Y <= I & "000" when S = "11" else

'0' & I & "00" when S = "10" else

"00" & I & '0' when S = "01" else

"000" & I;

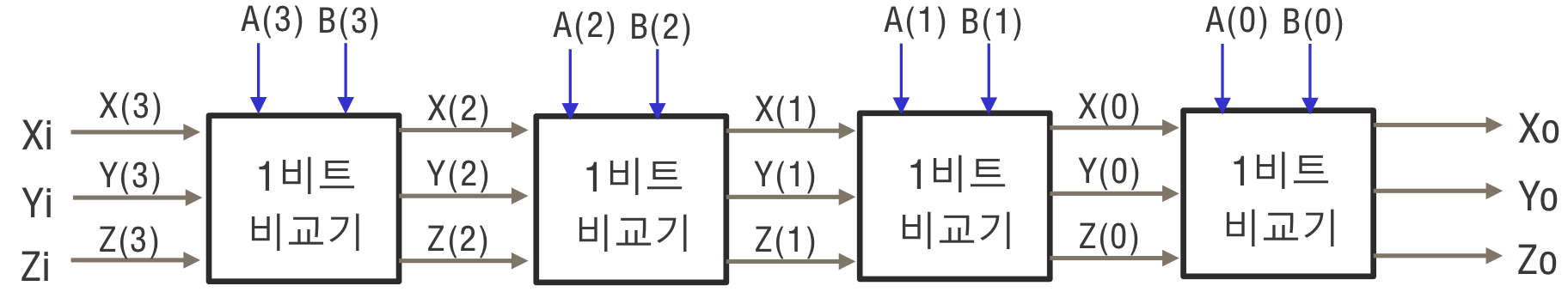

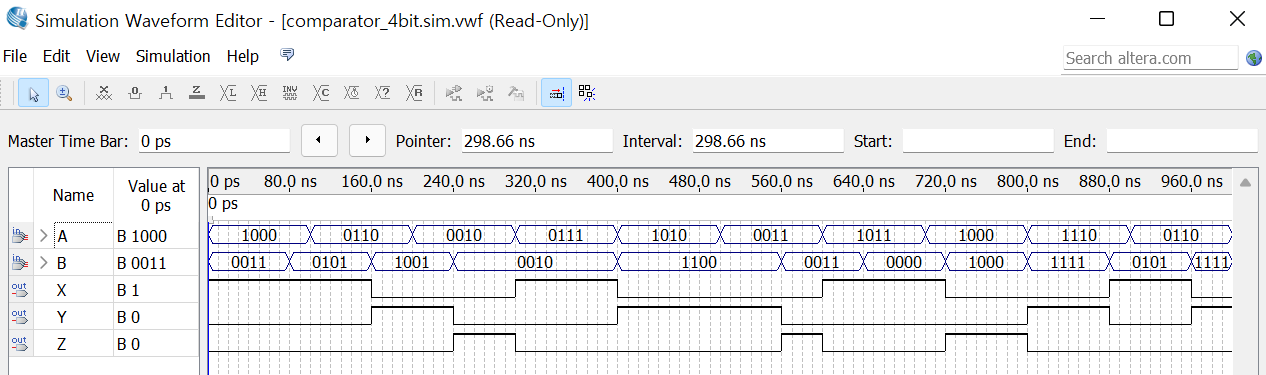

end dataflow;4비트 비교기

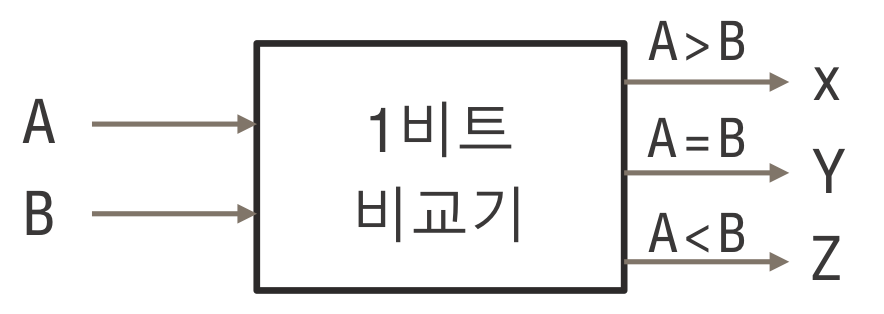

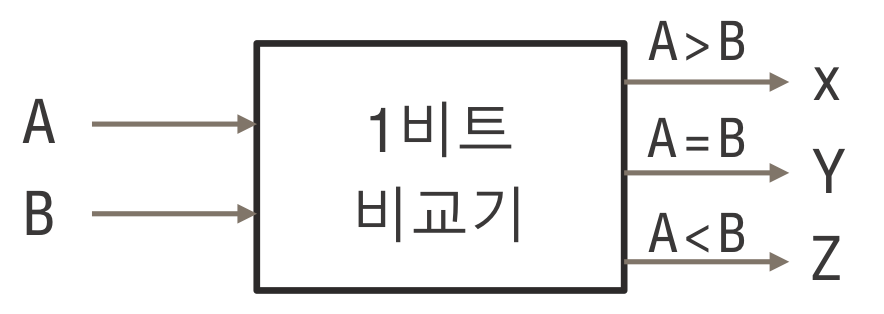

1) 1비트 비교기

- 4비트 비교기를 설계하는 방법으로 1비트 비교기를 직렬로 연결하여 만드는 방법이 있다.

- 따라서 1비트 비교기를 먼저 설계해야 한다.

- 1비트 비교기는 다음 논리회로와 같이 입력받은 두 수를 비교하여 어느수가 큰지, 작은지, 같은지를 판단한다.

위와같이 단순 비교를 하기 때문에 어렵지 않게 자료흐름적 모델링으로 다음과 같이 설계할 수 있다.

library ieee;

use ieee.std_logic_1164.all;

entity comparator_1bit is

port( a : in std_logic;

b : in std_logic;

x : out std_logic;

y : out std_logic;

z : out std_logic);

end comparator_1bit;

architecture dataflow of comparator_1bit is

begin

x <= a and(not b);

y <= a xnor b;

z <= (not a) and b;

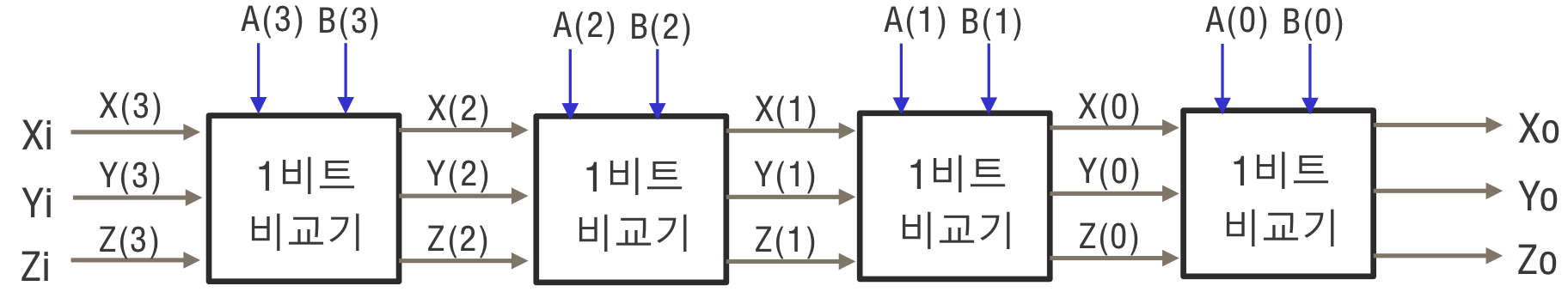

end dataflow;2) 4비트 비교기

- 1비트 비교기 4개를 직렬로 연결하여 구성할 수 있다.

- MSB부터 어느 한 수가 크다는 판별이 나면 다음 비교연산을 할 필요가 없다.

- 따라서 MSB부터 비교연산을 하여 판별되는 값을 다음 비교기로 넘겨주어 결과를 얻을 수 있다.

A와 B를 비교하여 A가 크면 X = 1, B가 크면 Y = 1, 두 값이 같으면 X = 1로 출력하도록 설계하면 다음과 같다.

library ieee;

use ieee.std_logic_1164.all;

entity comparator_4bit is

port( A : in std_logic_vector(3 downto 0);

B : in std_logic_vector(3 downto 0);

X : out std_logic;

Y : out std_logic;

Z : out std_logic);

end comparator_4bit;

architecture structural of comparator_4bit is

signal temp1_1, temp1_2, temp1_3 : std_logic;

signal temp2_1, temp2_2, temp2_3 : std_logic;

signal temp3_1, temp3_2, temp3_3 : std_logic;

component comparator_1bit is

port( in_a, in_b, in_x, in_y, in_z : in std_logic;

out_x,out_y,out_z : out std_logic);

end component;

begin

comp1: comparator_1bit port map( in_a => A(3),

in_b => B(3),

in_x => '0',

in_y => '0',

in_z => '1',

out_x => temp1_1,

out_y => temp1_2,

out_z => temp1_3);

comp2: comparator_1bit port map( in_a => A(2),

in_b => B(2),

in_x => temp1_1,

in_y => temp1_2,

in_z => temp1_3,

out_x => temp2_1,

out_y => temp2_2,

out_z => temp2_3);

comp3: comparator_1bit port map(A(1), B(1), temp2_1, temp2_2, temp2_3, temp3_1, temp3_2, temp3_3);

comp4: comparator_1bit port map(A(0), B(0), temp3_1, temp3_2, temp3_3, X, Y, Z);

end structural;'테크 > [verilog | VHDL]' 카테고리의 다른 글

| [VHDL] 4비트 병렬 가감산기(4-bit Full adder / subtractor) (0) | 2022.04.19 |

|---|---|

| [VHDL] 1비트 가감산기 설계(half / full, adder / subtractor) (0) | 2022.04.19 |

| [VHDL] 병렬문(Concurrent Statement) (0) | 2022.04.19 |

| [VHDL] 순차문 (0) | 2022.04.17 |

| [VHDL] 기본 문법 (0) | 2022.04.17 |

MUX(Multiplexer)

- 여러개 입력 중 제어신호에 의해 선택된 입력을 출력한다.

- 4x1 mux이라고 가정하면 input으로 4비트가 들어오고 제어신호에 의해 선택된 부분을 출력한다.

시뮬레이션 결과를 보면 input 4비트와 S라는 선택신호에 의해 00이면 0번비트, 01은 1번비트, 10은 2번, 11은 4번비트를 출력시키는 동작을 보여준다.

1) mux를 if문으로 작성하면 다음과 같다.

//if문

library ieee;

use ieee.std_logic_1164.all;

entity mux_4x1_vhdl is

port( I : in std_logic_vector(3 downto 0);

S : in std_logic_vector(1 downto 0);

Y : out std_logic);

end mux_4x1_vhdl;

architecture dataflow of mux_4x1_vhdl is

begin

process(I,S)

begin

if(S="11") then Y <= I(3);

elsif(S="10") then Y <= I(2);

elsif(S = "01") then Y <= I(1);

else Y <= I(0);

end if;

end process;

end dataflow;2) case문으로 작성하면

library ieee;

use ieee.std_logic_1164.all;

entity mux_4x1_behavioral_case is

port( I : in std_logic_vector(3 downto 0);

S : in std_logic_vector(1 downto 0);

Y : out std_logic);

end mux_4x1_behavioral_case;

architecture behavioral_case of mux_4x1_behavioral_case is

begin

process(I,S)

begin

case S is

when "11" => Y <= I(3);

when "10" => Y <= I(2);

when "01" => Y <= I(1);

when others => Y <= I(0);

end case;

end process;

end behavioral_case;3) when else 문(조건병행신호배정)으로 작성하면

// when ~ else문(조건병행신호배정)

library ieee;

use ieee.std_logic_1164.all;

entity mux_4x1_dataflow_when_else is

port( I : in std_logic_vector(3 downto 0);

S : in std_logic_vector(1 downto 0);

Y : out std_logic);

end mux_4x1_dataflow_when_else;

architecture dataflow of mux_4x1_dataflow_when_else is

begin

Y <= I(3) when S="11" else

I(2) when S="10" else

I(1) when S="01" else

I(0);

end dataflow;DEMUX(demultiplexer)

- mux와 반대로 하나의 입력신호와 제어신호에 의해 original신호의 몇번비트였는지 알려준다.

input으로 0이 들어오면 아무 값도 없기 때문에 S로 선택해도 0으로 출력되고 1이 들어오면 선택을 해서 특정 비트 위치에 1을 출력한다.

demux를 vhdl로 작성하면 다음과 같다.

1) if문 이용(순차)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_behavioral_if is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_behavioral_if;

architecture behavioral of demux_4x1_behavioral_if is

begin

process(I,S)

begin

if (S = "11") then Y <= I & "000";

elsif (S = "10") then Y <= '0' & I & "00";

elsif (S = "01") then Y <= "00" & I & '0';

else Y <= "000" & I;

end if;

end process;

end behavioral;2) case문 이용(순차)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_behavioral_case is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_behavioral_case;

architecture behavioral of demux_4x1_behavioral_case is

begin

process(I, S)

begin

case S is

when "11" => Y <= I & "000";

when "10" => Y <= '0' & I & "00";

when "01" => Y <= "00" & I & '0';

when others => Y <= "000" & I;

end case;

end process;

end behavioral;3) with ~ select ~ when(병렬)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_dataflow_with_select_when is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_dataflow_with_select_when;

architecture dataflow of demux_4x1_dataflow_with_select_when is

begin

with S select

Y <= "0001" when "00",

"0010" when "01",

"0100" when "10",

"1000" when "11",

null when others;

end dataflow;4) when ~ else(병렬)

library ieee;

use ieee.std_logic_1164.all;

entity demux_4x1_dataflow_when_else is

port( I : in std_logic;

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(3 downto 0));

end demux_4x1_dataflow_when_else;

architecture dataflow of demux_4x1_dataflow_when_else is

begin

Y <= I & "000" when S = "11" else

'0' & I & "00" when S = "10" else

"00" & I & '0' when S = "01" else

"000" & I;

end dataflow;4비트 비교기

1) 1비트 비교기

- 4비트 비교기를 설계하는 방법으로 1비트 비교기를 직렬로 연결하여 만드는 방법이 있다.

- 따라서 1비트 비교기를 먼저 설계해야 한다.

- 1비트 비교기는 다음 논리회로와 같이 입력받은 두 수를 비교하여 어느수가 큰지, 작은지, 같은지를 판단한다.

위와같이 단순 비교를 하기 때문에 어렵지 않게 자료흐름적 모델링으로 다음과 같이 설계할 수 있다.

library ieee;

use ieee.std_logic_1164.all;

entity comparator_1bit is

port( a : in std_logic;

b : in std_logic;

x : out std_logic;

y : out std_logic;

z : out std_logic);

end comparator_1bit;

architecture dataflow of comparator_1bit is

begin

x <= a and(not b);

y <= a xnor b;

z <= (not a) and b;

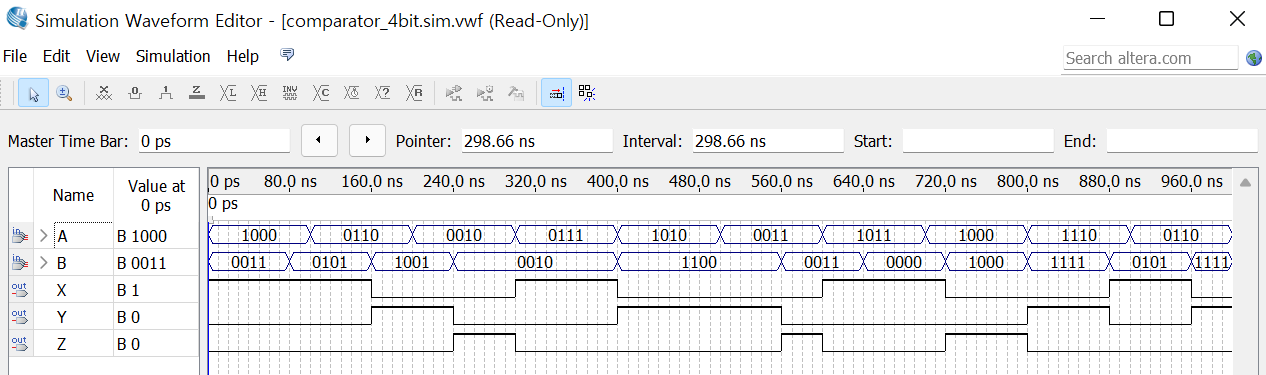

end dataflow;2) 4비트 비교기

- 1비트 비교기 4개를 직렬로 연결하여 구성할 수 있다.

- MSB부터 어느 한 수가 크다는 판별이 나면 다음 비교연산을 할 필요가 없다.

- 따라서 MSB부터 비교연산을 하여 판별되는 값을 다음 비교기로 넘겨주어 결과를 얻을 수 있다.

A와 B를 비교하여 A가 크면 X = 1, B가 크면 Y = 1, 두 값이 같으면 X = 1로 출력하도록 설계하면 다음과 같다.

library ieee;

use ieee.std_logic_1164.all;

entity comparator_4bit is

port( A : in std_logic_vector(3 downto 0);

B : in std_logic_vector(3 downto 0);

X : out std_logic;

Y : out std_logic;

Z : out std_logic);

end comparator_4bit;

architecture structural of comparator_4bit is

signal temp1_1, temp1_2, temp1_3 : std_logic;

signal temp2_1, temp2_2, temp2_3 : std_logic;

signal temp3_1, temp3_2, temp3_3 : std_logic;

component comparator_1bit is

port( in_a, in_b, in_x, in_y, in_z : in std_logic;

out_x,out_y,out_z : out std_logic);

end component;

begin

comp1: comparator_1bit port map( in_a => A(3),

in_b => B(3),

in_x => '0',

in_y => '0',

in_z => '1',

out_x => temp1_1,

out_y => temp1_2,

out_z => temp1_3);

comp2: comparator_1bit port map( in_a => A(2),

in_b => B(2),

in_x => temp1_1,

in_y => temp1_2,

in_z => temp1_3,

out_x => temp2_1,

out_y => temp2_2,

out_z => temp2_3);

comp3: comparator_1bit port map(A(1), B(1), temp2_1, temp2_2, temp2_3, temp3_1, temp3_2, temp3_3);

comp4: comparator_1bit port map(A(0), B(0), temp3_1, temp3_2, temp3_3, X, Y, Z);

end structural;'테크 > [verilog | VHDL]' 카테고리의 다른 글

| [VHDL] 4비트 병렬 가감산기(4-bit Full adder / subtractor) (0) | 2022.04.19 |

|---|---|

| [VHDL] 1비트 가감산기 설계(half / full, adder / subtractor) (0) | 2022.04.19 |

| [VHDL] 병렬문(Concurrent Statement) (0) | 2022.04.19 |

| [VHDL] 순차문 (0) | 2022.04.17 |

| [VHDL] 기본 문법 (0) | 2022.04.17 |